The next release of Box64 is finally out. Many fixes, a new Dynarec backend and Vulkan overlay support… Let’s dig in. Many fixes and improvements to Dynarec A lot of work has been done to fix issues. It can be in the dynarec where many opcodes got their behavior fixed, or many speed regressions introduced…

Tag: box64

Happy new year, and happy new release of Box64! The new version brings a ton of new enhancements and fixes to all 3 supported platforms, with Steam running not only on Arm64, but also on RiSC-V and on Loongarch! And this is the Linux version of Steam, not the Windows one (but the Windows one…

And a new release of Box64 is tagged. v0.3.8 has a new DynaCache feature and a ton of fixes and improvements to dynarec & wrappers. Lets dig in. Fixes everywhere There are numerous fixes everywhere in this release. Dynarec opcodes, wrappers, memory tracking and management. All those fixes, along with more wrapped function have improved…

New Box64 v0.3.4 released

A new released of Box64 appeared. While previous version introduced lots of new features, this version is more of a stabilisation released. For example, last version introduced Native Flags, this version fixed many bugs introduced with it. So more things are now running. Same for Box32. Many fixes have been done and box32 is running…

A new version of both box64 and box86 has been released! While the changelog for box86 doesn’t contain much, there are a lot of new improvements, features and fixes for box64. With some speed increase, improved compatibility and a new subproject, box32, there is a lot. But let’s dive into more details on the performances…

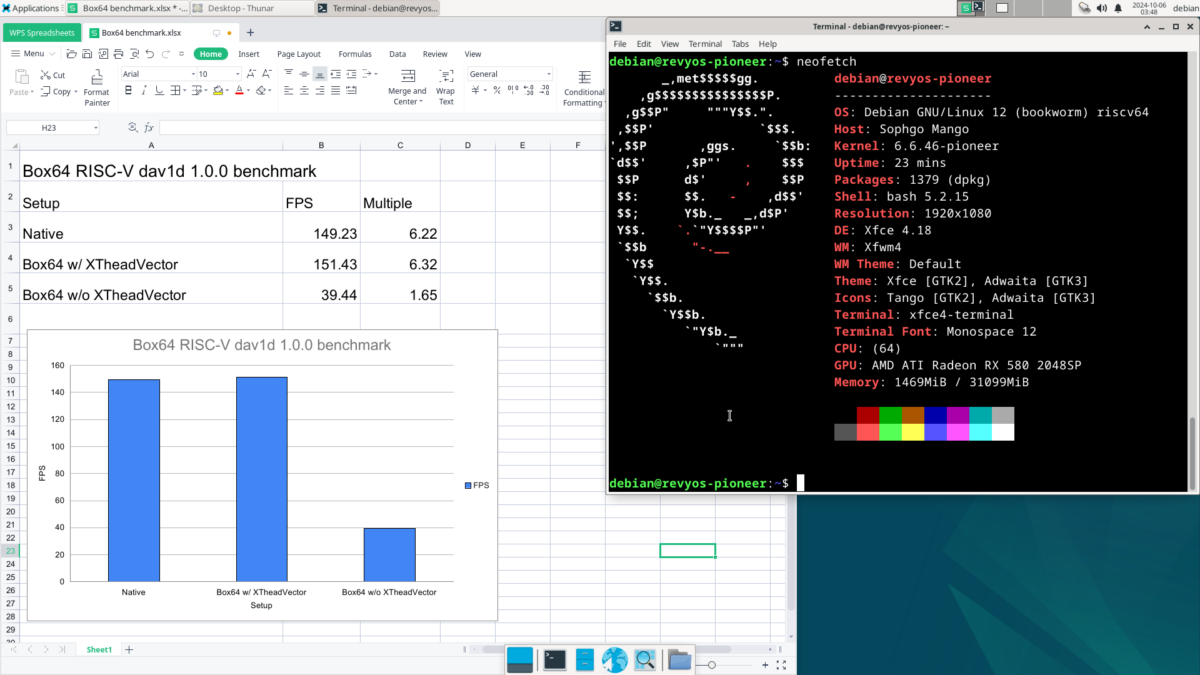

Utilizing RVV and More!

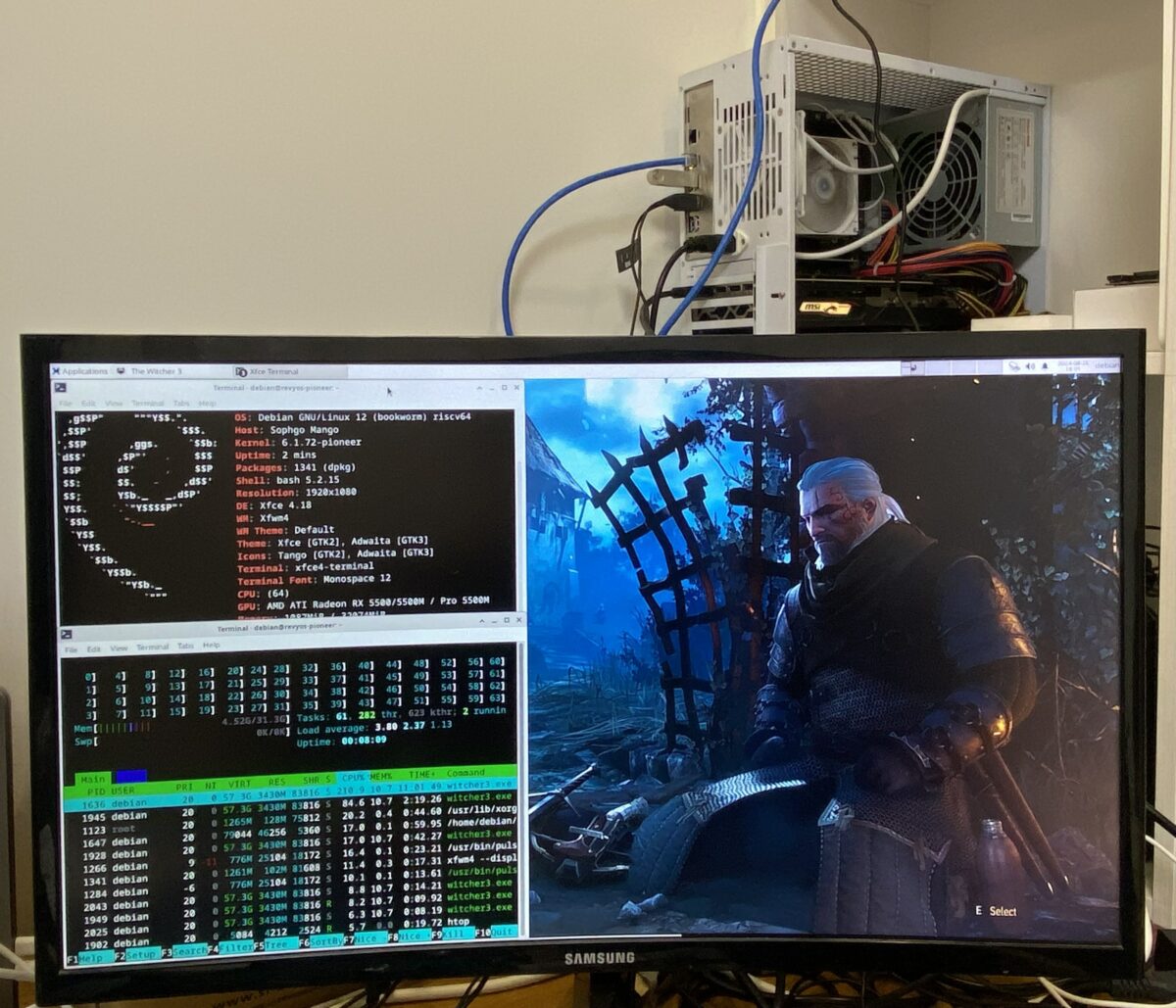

What It Takes to Run The Witcher 3 on RiSC-V

Since the last post about it, the dynarec (dynamic recompiler, a Just-In-Time recompilation of x86 code) changed a lot. It still works in four major steps, but now there are a lot more intermediary steps. So let’s see how it works now! Note: this article will focus on the ARM version of the dynarec on…

Note: this article is pretty technical. Basic understanding of what registers are is a strict minimum required to understand what follows. What is AVX? AVX (and its extension AVX2) are complex x86_64 instruction sets which extends the SSE4 instruction set. It mandates the existence of extensions of the 16 SSE 128-bits-wide XMM registers (called XMM0…

In a previous post, we talked about the mechanism behind library wrapping. In it, I said box86/box64 used some manually written files to correctly call functions. However, there is a big question: how are these files written? To follow this article, you will need at least a basic understanding of function signatures. The basics First,…